# Argentina \$ 27.- // México \$ 54.-TÉCNICO en ELECTRONICA

CONCEPTOS FUNDAMENTALES Y PRÁCTICA PROFESIONAL

# Electrónica digital y compuertas lógicas

- Sistema binario

- Mapas de Karnaugh

- Compuertas lógicas

- **Circuitos** combinacionales

# **TÉCNICO** en

CONCEPTOS FUNDAMENTALES Y PRÁCTICA PROFESIONAL

#### Coordinación editorial

Paula Budris

#### Asesores técnicos

Federico Pacheco

#### **Nuestros expertos**

Diego Aranda Esteban Aredez Alejandro Fernández

Lucas Lucyk

Luis Francisco Macías

Mauricio Mendoza

Norberto Morel

David Pacheco

Federico Pacheco

Gerardo Pedraza

Mariano Rabioglio

Luciano Redolfi

Alfredo Rivamar

Federico Salguero

Técnico en electrónica es una publicación de Fox Andina en coedición con Dálaga S.A. Esta publicación no puede ser reproducida ni en todo ni en parte, por ningún medio actual o futuro sin el permiso previo y por escrito de Fox Andina S.A. Distribuidores en Argentina: Capital: Vaccaro Sánchez y Cía. S.C., Moreno 794 piso 9 (1091), Ciudad de Buenos Aires, Tel. 5411-4342-4031/4032; Interior: Distribuidora Interplazas S.A. (DISA) Pte. Luis Sáenz Peña 1832 (C1135ABN), Buenos Aires, Tel. 5411-4305-0114. Bolivia: Agencia Moderna, General Acha E-0132, Casilla de correo 462, Cochabamba, Tel. 5914-422-1414. Chile: META S.A., Williams Rebolledo 1717 - Ñuñoa - Santiago, Tel. 562-620-1700. Colombia: Distribuidoras Unidas S.A., Carrera 71 Nro. 21 - 73, Bogotá D.C., Tel. 571-486-8000. Ecuador: Disandes (Distribuidora de los Andes) Calle 7° y Av. Agustín Freire, Guayaquil, Tel. 59342-271651. México: Distribuidora Intermex, S.A. de C.V., Lucio Blanco #435, Col. San Juan Tlihuaca, México D.F. (02400), Tel. 5255 52 30 95 43. Perú: Distribuidora Bolivariana S.A., Av. República de Panamá 3635 piso 2 San Isidro, Lima, Tel. 511 4412948 anexo 21. Uruguay: Espert S.R.L., Paraguay 1924, Montevideo, Tel. 5982-924-0766. Venezuela: Distribuidora Continental Bloque de Armas, Edificio Bloque de Armas Piso 9no., Av. San Martín, cruce con final Av. La Paz, Caracas, Tel. 58212-406-4250.

Impreso en Sevagraf S.A. Impreso en Argentina. Copyright © Fox Andina S.A. VI, MMXIII.

#### Anónimo

Técnico en electrónica / Anónimo ; coordinado por Paula Budris. -1a ed. - Buenos Aires: Fox Andina; Dalaga, 2013.

> 576 p.; 27x19 cm. - (Users; 23) ISBN 978-987-1949-14-4 1. Informática. I. Budris, Paula, coord. II. Título. CDD 005.3

## En esta clase veremos...

NUESTRO PRIMER ACERCAMIENTO A LA ELECTRÓNICA DIGITAL Y LAS COMPUERTAS LÓGICAS; TAMBIÉN PRESENTAREMOS LAS TÉCNICAS QUE DEBEN CONOCERSE PARA TRABAJAR CON ESTE TIPO DE SEÑALES.

Aquí comenzaremos a introducirnos en un área de la electrónica llamada digital, que se diferencia de la analógica por no trabajar con señales de esta clase. La electrónica digital se basa en el uso de señales del tipo digital y sistemas del tipo binario, que codifican información que luego será interpretada y procesada.

En esta línea, veremos primero una explicación de los sistemas de numeración decimal, octal, hexadecimal y binario; luego distintos sistemas binarios, como Gray, BCD, y exceso 3, y la forma de realizar conversiones entre los diferentes sistemas. Además explicaremos las compuertas lógicas, sus tablas de verdad, simbología, características, y la combinación de compuertas para armar circuitos lógicos más complejos.

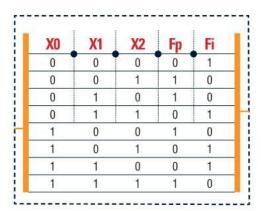

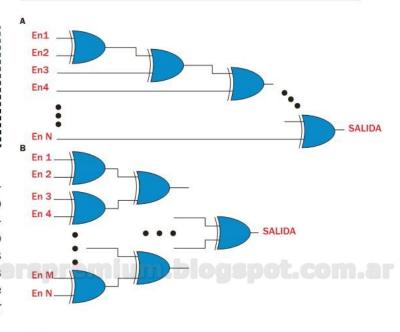

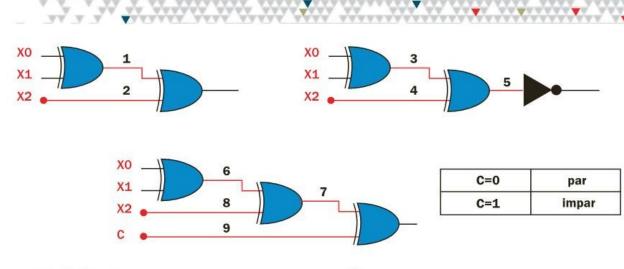

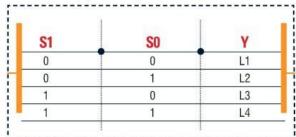

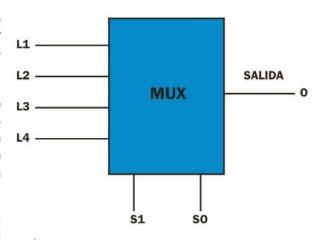

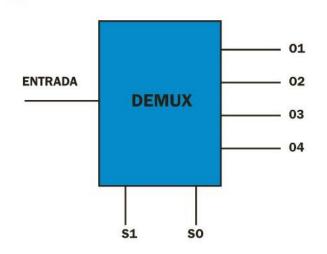

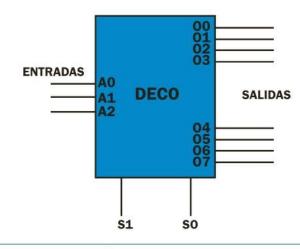

Finalmente, veremos los circuitos combinacionales, entre los cuales se presentarán: el generador y detector de paridad, el multiplexor y demultiplexor, el codificador y decodificador, los conversores de código, y los comparadores. De ellos veremos los usos, diagramas, tablas de verdad y circuitos.

#### **SUMARIO**

FUNDAMENTOS DE TÉCNICAS DIGITALES

Sistemas de numeración y teorías relacionadas.

COMPUERTAS LÓGICAS

Características y familias lógicas.

CIRCUITOS COMBINACIONALES

Conoceremos diferentes circuitos, como el multiplexor y el codificador.

2 Clase 11 //

# FUNDAMENTOS DE TÉCNICAS DIGITALES

LA ELECTRÓNICA FÍSICA CONSTA DE ELEMENTOS PREFABRICADOS QUE PODEMOS ADQUIRIR E INSTALAR SEGÚN LAS ESPECIFICACIONES, PERO, PARA SELECCIONARLOS, PRIMERO DEBEMOS ENTENDER SU FUNCIONAMIENTO.

## Sistema binario

Antes de empezar a entender el funcionamiento de nuestros equipos digitales, necesitamos conocer su lenguaje de comunicación. Los seres humanos nos comunicamos en lenguajes predeterminados, como español, inglés portugués, francés, entre otros. Las máquinas utilizan como lenguaje el sistema binario.

Para entender el sistema binario, necesitamos introducir los sistemas de numeración que fueron aplicados previamente (incluso algunos sistemas aún los emplean) para concluir en el binario.

Uno de los primeros sistemas utilizados es el decimal que es el que manejamos a diario. Posee como base 10 dígitos diferentes que les corresponden al 0, 1, 2, 3, 4, 5, 6, 7, 8 y 9. Recibe el nombre de **sistema decimal** por herencia de los árabes e hindúes, quienes aplicaron este sistema a la numeración, basado en los dígitos de la mano principalmente para establecer una relación fácil de recordar. Este sistema es denominado posicional ya que el dígito representa el valor que se le asigna, dependiendo de su posición. El sistema decimal es un sistema en el que el valor de cada dígito depende de su lugar dentro del número.

Debemos tener en cuenta que, a partir de esta configuración, obtenemos los números enteros. Por

ejemplo, para obtener el número 695 es necesario efectuar las operaciones que vemos a continuación:

$$102.6 + 101.9 + 100.5 =$$

=  $600 + 90 + 5 =$

=  $695$

El sistema numérico utilizado como variante del decimal fue el sistema octal. Está basado en 8 dígitos (0, 1, 2, 3, 4, 5, 6 y 7). Posee dos caracteres menos que el decimal, lo que permite agruparlos en menores combinaciones.

Consideremos que el valor del sistema octal es el mismo que el del decimal y se utilizaba para evitar contar los dedos pulgares de la mano.

LAS CONVERSIONES DE SISTEMAS

NUMÉRICOS POSIBILITARON LA

AGRUPACIÓN DE INFORMACIÓN EN

BYTES, LENGUAJE COMPUTACIONAL.

// Clase 11 -

|          |               | Billo    | ones     |              |           |          |               | Mille    | ones            |              |          |          |         | Unid            | ades     |         |          |   |

|----------|---------------|----------|----------|--------------|-----------|----------|---------------|----------|-----------------|--------------|----------|----------|---------|-----------------|----------|---------|----------|---|

| M        | illar<br>bill | es<br>ón | Un<br>de | idad<br>bill | les<br>ón |          | illar<br>mill |          |                 | idad<br>bill |          | M        | illar   | es              | Un       | idad    | les      |   |

| Centenas | Decenas       | Unidades | Centenas | Decenas      | Unidades  | Centenas | Decenas       | Unidades | Centenas        | Decenas      | Unidades | Centenas | Decenas | Unidades        | Centenas | Decenas | Unidades |   |

| W        | W             | W        | re       | 36           | ug<br>    | 30       | rs            | PF       | <b>@</b> 1      | ni           | u        | n.       | b.      | 0               | JS       | pe      | t.       | C |

| 1017     | 1016          | 1015     | 1014     | 1013         | 1012      | 1011     | 1010          | 109      | 10 <sup>8</sup> | 10           | 106      | 105      | 104     | 10 <sup>3</sup> | 102      | 101     | 100      | - |

El sistema decimal es el más usado en el ámbito de la educación. Se trata del primer sistema numérico que aprendemos.

#### **Convertir Decimal a octal**

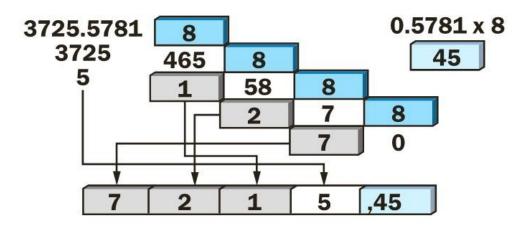

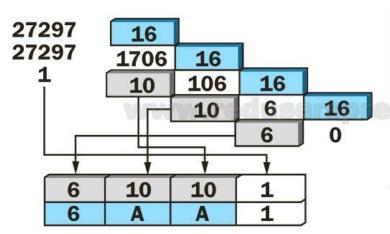

Diagrama de conversión decimal a octal mediante sustitución por restos.

Es utilizado en la informática para reemplazar al sistema **hexa- decimal**, para utilizar números enteros en lugar de letras, como veremos más adelante. Se utiliza además para abreviar los números binarios que emplean caracteres de 6 bits. Cada 3 bits es convertido en un único dígito octal.

Como mencionamos antes, el sistema octal se utiliza para reemplazar, en determinadas, ocasiones al sistema hexadecimal.

Este último sistema utiliza 16 símbolos sin repetir (de ahí el prefijo *hexa* representativo). Se usa principalmente en el mundo de la informática, ya que la unidad de trabajo es el byte, que representa al octeto de bits como unidad de memoria.

7.83 + 2.82 + 1.81 + 5.80 + 4.8-1 + 5.8-2 = = 7.512 + 2.64 + 5.1 + 4.0,125 + 5.0,015625 = = 3584 + 128 + 5 + 0,5 + 0,078125 = = 3725,578125 7215,45q = 3717,578125d

(La letra q indica que es un número expresado en octal).

Posee por convención 16 caracteres (0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F), y está basado en el sistema decimal de diez dígitos y seis letras. Las letras seleccionadas corresponden a las primeras seis del alfabeto latino, a las que se les asigna el correspondiente valor de: A = 10, B = 11, C = 12, D = 13, E = 14, F = 15. También es un sistema de numeración posicional, en el cual el valor de cada factor numérico se ve alterado dependiendo de la posición que este ocupe dentro de la cadena de números, multiplicado por la base del sistema (en este caso 16), elevado al exponente de la posición que ocupe. Ejemplificamos con 6AA116:

#### Convertir decimal a hexadecimal

6.163 + A.162 + A.161 + 1.160 = = 6.4096 + 10.256 + 10.16 + 1.1 = = 24576 + 2560 + 160 + 1 = = 27297 6AA116 = 27297

Procedimiento para pasar del sistema decimal al hexadecimal. Los restos deben ser convertidos a letras hexadecimales si corresponde.

Para realizar operaciones con sistema hexadecimal, debemos tener en cuenta determinadas consideraciones. Recordemos que existe un límite, al igual que en el decimal, para realizar operaciones. Ejemplifiquemos una operación de suma.

Recordemos las reglas previamente comentadas y, al realizar operaciones numéricas correspondientes, no olvidemos que los dos únicos valores permitidos serán 1 y 0. Por lo que la suma

$$7 + 7 = 14 = E$$

$B + 1 = 11 = C$

$$9 + 8 = 17$$

(17 no está en la escala hexadecimal, recordemos que el máximo es F = 15). Corregimos 17 - 16 = 1; como superamos una vez el límite, tenemos 1 excedente. Entonces:

$$9+8=11$$

(En hexadecimal 17 = 11).

$7+7=14=E$

$F+E=(15+14=29; 29-16=13; 1 13; 1D) 1D$

En la actualidad, podemos realizar estas operaciones en calculadoras científicas reduciendo el engorroso trabajo de recordar todos los métodos, pero aun así es importante entender cómo funciona. Quizás el sistema numérico más utilizado en el mundo de la computación sea el sistema binario, ya que toda la codificación electrónica y de programación se encuentra basada en este sistema.

Para representar los números en el sistema binario, utilizamos solo dos caracteres: el 0 y el 1. En electrónica, los valores de 0 y 1 los utilizamos para establecer dos estados, encendido y apagado, dos niveles: ese es el principio de funcionamiento de la mayoría de los dispositivos actuales.

El sistema de representación está basado, al igual que los sistemas anteriores, en formato posicional de la base elevado al exponente que representa su posición en la cadena numérica. Por ejemplo, un número en binario 10011b lo convertimos mediante: Fórmula 1.

DE SISTEMAS **NUMÉRICOS** POSIBILITARON LA se resumirá a: Fórmula 2. AGRUPACIÓN DE INFORMACIÓN EN BYTES, LENGUAJE

Fórmula 1

$$1.24 + 0.23 + 0.22 + 1.21 + 1.20 =$$

=  $16 + 0 + 0 + 2 + 1 =$

= 19

LAS CONVERSIONES

COMPUTACIONAL.

Con estas condiciones, se pueden realizar las operaciones aritméticas siguientes, respetando las reglas.

Existen sistemas binarios que difieren en algunas reglas en particular, que definen nuevos sistemas o códigos. Son utilizados, generalmente, en teorías digitales. El primero es conocido como Código Gray.

#### Fórmula 2

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1+1=10 (2 no es un valor permitido, por lo que el primer valor volverá a 0 y se le asignará un segundo lugar, se le adiciona el 1).

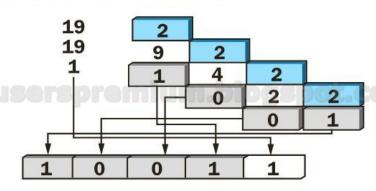

#### Convertir decimal a binario

Conversión de decimal a números binarios. Siempre se debe comprobar la conversión en un sentido como en el otro.

## 6

►Clase 11 //

El sistema Gray (también conocido como sistema binario reflejado) es un código binario en el que dos valores sucesivos solo se diferencian en uno de sus dígitos. Se utilizó para prevenir señales erróneas en los switches electromecánicos. Actualmente, se utiliza en sistemas de televisión por cable y telecomunicaciones como sistema de corrección de errores. El sistema surge a partir del código binario convencional mediante un proceso reflejante que permite generar una secuencia de permutación cíclica.

El método conocido como código Gray consiste en tomar señales analógicas y convertirlas a grupos de códigos binarios, modificando solo un valor que garantice que cualquier transmisión variará solo en un bit. La ventaja de utilizar este método reside en que tiene un diseño eficiente, práctico y veloz.

Los sistemas de computación utilizan un estándar para representar números decimales en binario, conocido como BCD (Binary-Coded Decimal), en el que cada decimal es representado por un binario de 4 bits y no como un número binario puro. Con los decimales codificados, podemos realizar todas las operaciones matemáticas sin incurrir en las tediosas conversio-

#### Tablas comparativas de sistemas numéricos digitales

| Decimal | Octal | Hexa-<br>decimal | Binario |

|---------|-------|------------------|---------|

| 1       | 1     | 1                | 00001   |

| 2       | 2     | 2                | 00010   |

| 3       | 3     | 3                | 00011   |

| 4       | 4     | 4                | 00100   |

| 5       | 5     | 5                | 00101   |

| 6       | 6     | 6                | 00110   |

| 7       | 7     | 7                | 00111   |

| 8       | 10    | 8                | 01000   |

| 9       | 11    | 9                | 01001   |

| 10      | 12    | Α                | 01010   |

| 11      | 13    | В                | 01011   |

| 12      | 14    | C                | 01100   |

| 13      | 15    | D                | 01101   |

| 14      | 16    | E                | 01110   |

| 15      | 17    | F                | 01111   |

| 16      | 20    | 10               | 10000   |

| 17      | 21    | 11               | 10001   |

| 18      | 22    | 12               | 10010   |

| 19      | 23    | 13               | 10011   |

| 20      | 24    | 14               | 10100   |

Tabla comparativa entre los cuatro sistemas estudiados. Se puede continuar su llenado utilizando los métodos ya descriptos.

#### **PARTE FRACCIONARIA**

En todos los sistemas numéricos, podemos tratar con partes enteras y partes decimales. Estas partes decimales son tratadas de la misma manera que las enteras con la diferencia que los exponentes se reemplazan por números negativos relacionados con la posición que estos ocupan en la cadena de caracteres. De la coma a la izquierda, son considerados positivos; a la derecha, negativos. Otro método es la multiplicación de la parte fraccionaria por el representativo del sistema y reduciendo a su correspondiente factor.

nes que, por lo general, nos acarrean demasiados errores en el momento de hacer operaciones complejas. Remarcamos que las operaciones en BCD entregan decimales en binarios de 4 bits por separado y no una cadena de números binarios, por lo que el sistema sirve para representar cifras, no al número en su totalidad El código Exceso 3 es un derivado de BCD donde se le suma 3 (en binario) a cada dígito decimal y, luego, se lo convierte en un número binario de 4 bits.

Los distintos códigos surgen a partir de la necesidad de simplificar las operaciones y las posteriores codificaciones. La tec-

EL CÓDIGO BINARIO SE UTILIZÓ PARA

REPRESENTAR DOS ESTADOS DE LA

ELECTRÓNICA DE VÁLVULA ABIERTA (1)

Y VÁLVULA CERRADA (0).

nología se aceleró gracias a los métodos cada vez más eficaces para realizar operaciones aritméticas y, así, llevar a cabo operaciones digitales como las conocemos hoy.

## Lógica binaria y álgebra de Boole

Las operaciones donde se implican números binarios comprenden ciertas reglas; como en la aritmética, llamamos álgebra a la suma, resta, multiplicación y división, pero la lógica binaria realiza estas operaciones según sus propias reglas. Los procesadores de los dispositivos electrónicos realizan estas operaciones denominadas **lógicas** con los datos contenidos en los programas que lo soliciten. A diferencia de las operaciones aritméticas en las que los resultados son valores numéricos, las operaciones lógicas nos entregan dos resultados que pueden ser leídos como **VERDADERO** o **FALSO**.

Operación unitaria (conocida como complemento)

Se conoce como tal a todo elemento (a) de un conjunto A que le corresponda otro elemento distinto

(b) del mismo conjunto A tal que se cumpla que el segundo sea el complemento del primero.

a = -b Ej: 8 = -8

### CALCULADORAS CIENTÍFICAS

La calculadora científica puede ser de gran ayuda para efectuar operaciones complejas.

En todas las versiones de Windows, encontramos la calculadora científica como aplicativo base.

La calculadora base del sistema operativo Windows viene con una configuración básica, pero, mediante el menú Ver – Programador, obtendremos nuevas opciones para el cálculo en distintos sistemas numéricos: hexadecimal, decimal, octal y binario. La ventaja de esta calculadora es que podremos realizar operaciones aritméticas sin realizar ningún tipo de conversión previa.

|             | Binario                       | Decimal                          | Octal                      | Hexadecimal                  |

|-------------|-------------------------------|----------------------------------|----------------------------|------------------------------|

| Binario     |                               | Fórmula<br>Polinómica<br>Pot. 2  | Agrupar de a<br>3 bits     | Agrupar de a<br>4 bits       |

| Decimal     | Entera/2<br>Fraccionaria/2    |                                  | Entera/8<br>Fraccionaria/8 | Entera/16<br>Fraccionaria/16 |

| Octal       | C/dígito en<br>binario 3 bits | Fórmula<br>polinómica<br>Pot. 8  | remium.                    | Pasar por binario            |

| Hexadecimal | C/dígito en<br>binario 4 bits | Fórmula<br>polinómica<br>Pot. 16 | Pasar por binario          |                              |

#### Operación binaria (llamada suma y producto)

Debemos tener en cuenta que se define como tal operación al resultado de todo par ordenado (a, b) de elementos únicos de un conjunto A que le corresponda un único valor c como resultado de sumar los elementos del par ordenado, tal como vemos a continuación:

$$a + b = c$$

Ej:  $3 + 4 = 7$

Al producto del resultado c, como la multiplicación de los elementos del par ordenado.

$$a.b = c Ej: 3.4 = 12$$

#### Operaciones nulas

Se define como operación nula al único resultado de multiplicar cualquier elemento del conjunto A por el número 0 que resulta siempre igual a 0.

$$a.0 = 0$$

Ej:  $3.0 = 0$

#### **TABLA DE VERDAD**

| 2 | W                     |                     |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---|-----------------------|---------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| q | r                     | ٦r                  | p⊸q                       | ((p→q) v¬r)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V | V                     | F                   | V                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ٧ | F                     | V                   | V                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| F | ٧                     | F                   | F                         | F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| F | F                     | V                   | F                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ٧ | ٧                     | F                   | V                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V | F                     | V                   | V                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| F | ٧                     | F                   | V                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| F | F                     | V                   | V                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | V<br>F<br>F<br>V<br>F | V V F F V V V F F V | V V F V F V F V F V F V F | V V F V V F V V F F F V F V V F V V F V V F V V F V V F V V F V V F V V F V V F V V F V V F V V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F V F F V F V F F F F F F V F F F F F F V F F F F F F F F V F F F F F F F |

Las tablas de verdad basadas en proposiciones son utilizadas para organizar los resultados de las operaciones algebraicas.

Las tablas de verdad son utilizadas para mostrar el valor de verdad de una proposición compuesta, es decir, determina el grado de verdad que posea cierta expresión para cada combinación de valores que se le pueda asignar a los componentes.

Para armar la tabla de verdad, se establece el sistema o definición, y las variables se asumen según el resultado.

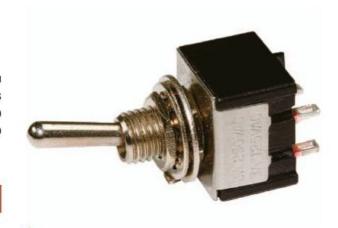

Los interruptores de dos posiciones cumplen la función de verdadero y falso, o abierto y cerrado, que en binario será 0 y 1.

Las operaciones booleanas responden a determinados **axiomas** que deben respetar. Para definir a una operación como perteneciente al álgebra de Boole, debe cumplir con:

- V Ley asociativa de la suma. Si a, d y c pertenecen al conjunto A, entonces se debe cumplir que (a + b) + c = a + (b + c).

- ▼ Ley asociativa del producto. Si a, d y c pertenecen al conjunto A, entonces se debe cumplir que (a \* b) \* c = a \* (b \* c).

- $\nabla$  Existe elemento nulo en la suma. Si a pertenece al conjunto A, entonces se debe cumplir que a + 0 = a.

- $\blacksquare$  Existe elemento neutro en el producto. Si a pertenece al conjunto A, entonces se debe cumplir que a \* 1 = a.

- ▼ Ley conmutativa de la suma. Si a y b pertenecen al conjunto A, entonces se debe cumplir que a + b = b + a.

- $\blacktriangledown$  Ley conmutativa del producto. Si a y b pertenecen al conjunto A, entonces se debe cumplir que a \* b = b \* a.

- ▼ Ley distributiva de la suma respecto del producto. Si a, b y c pertenecen al conjunto **A**, entonces se debe cumplir que a + (b \* c) = (a + b) \* (a + c).

- ► Ley distributiva del producto respecto a la suma. Si a, b y c pertenecen al conjunto A, entonces se debe cumplir que a \* (b + c) = (a \* b) + (a \* c).

- $\nabla$  Existe elemento complemento para la suma. Si a pertenece al conjunto A, entonces existe un -a, que cumple a + (-a) = 1.

- ightharpoonup Existe elemento complemento para el producto. Si a pertenece al conjunto A, entonces existe un -a , que cumple a \* (-a) = 0.

| Propiedades       | Intersección                                     | Unión                                            |

|-------------------|--------------------------------------------------|--------------------------------------------------|

| Conmutativa       | A∩B = B∩A                                        | A∪B = B∪A                                        |

| Asociativa        | A∩(B∩C) = (A∩B)∩C                                | $A \cup (B \cup C) = (A \cup B) \cup C$          |

| Idempotente       | A ∩ A = A                                        | A∪A = A                                          |

| Simplificación    | A ∩ (B ∪ A) = A                                  | A ∪ (B ∩ A) = A                                  |

| Distributiva      | $A \cap (B \cup C) = (A \cap B) \cup (A \cap C)$ | $A \cup (B \cap C) = (A \cup B) \cap (A \cup C)$ |

| Elementos neutros | A∩E = A                                          | A∩Ø = A                                          |

| Absorción         | A ∩ Ø = Ø                                        | AUE = E                                          |

Simbólicamente, las leves se representan según su función, no se utilizan números, se utilizan símbolos representativos.

A partir de los axiomas, podemos demostrar los teoremas fundamentales del álgebra:

- Ley de idempotencia para la suma implica que, para todo a perteneciente al conjunto A, se aplica a + a = a.

- Ley de idempotencia para el producto implica que, para todo a perteneciente al conjunto A, se aplica lo que ejemplificamos a continuación: a \* a = a.

- ▼ Ley de absorción para la suma implica que, para todo a perteneciente al conjunto A, se aplica de la siguiente forma: a + 1 = 1.

- ▼ Ley de absorción para el producto implica que, para todo a perteneciente al conjunto A, se aplica a \* 0 = 0.

- Ley de identidad para la suma implica que, para todo a perteneciente al conjunto A, se aplica a + 0 = a.

- Ley de identidad para el producto implica que, para todo a perteneciente al conjunto A, se aplica a \* 1 = a.

- Ley de involución implica que, para todo a perteneciente al conjunto A, se aplica lo que mostramos a continuación: -(-a) = a.

- ▼ Ley del complemento implica que, para todo a perteneciente al conjunto A, se aplica que -1 = 0; -0 = 1

- Leves de De Morgan implican que. para todo a y b perteneciente al conjunto A, se aplica que – (a + b) = -a \* -b(a \* b) = -a + -b

## Mapas de Karnaugh

Cuando se realiza el cálculo de funciones booleanas, las operaciones pueden volverse muy tediosas y también complejas. Los mapas Karnaugh se empezaron a aplicar ante la necesidad de facilitar la resolución de estos inconvenientes y se convirtieron en una herramienta muy utilizada para la simplificación de circuitos lógicos.

El sistema utiliza técnicas que realiza el cerebro humano para detectar patrones y formas analíticas de reconocer, identificar y eliminar condiciones determinadas, minimiza expresiones del tipo

10

►Clase 11 //

suma de productos y producto de sumas. Simplifica expresiones booleanas a mínimas cadenas, de modo que no exista otra con menor número de operaciones minimizando la cantidad de variables.

Previo a los mapas Karnaugh (de ahora en más los llamaremos **MK**) se utilizaban las tablas de verdad para obtener la función expresada por suma de productos. Con los MK, representamos la función deseada para obtener la respuesta directamente utilizando una **tabla de verdad bidimensional** (de dos entradas, verticales y horizontales).

Otorgamos jerarquía a los operadores siempre que cumplan que  $\mathbf{a} < \mathbf{b}$  si se cumple que:

$$a + b = b$$

$a \cdot b = a$

$-a + b = 1$

$a \cdot -b = 0$

Según el conjunto de números binarios, a=0 y b=1; entonces comprobamos que las afirmaciones anteriores son correctas.

| Ley de Identidad  | $\begin{array}{c} \mathbf{A} = \mathbf{A} \\ \overline{\mathbf{A}} = \overline{\mathbf{A}} \end{array}$ |

|-------------------|---------------------------------------------------------------------------------------------------------|

| I 0t-th           | A . B = B . A                                                                                           |

| Ley Conmutativa   | A + B = B + A                                                                                           |

| Lav. Assalativa   | A.(B.C) = B.A.C                                                                                         |

| Ley Asociativa    | A + (B + C) = B + A + C                                                                                 |

| 1 l-l             | A . A = A                                                                                               |

| Ley idempotencia  | A + A = A                                                                                               |

| Ley doble         | ión $\overline{\overline{A}} = A$                                                                       |

| negativo/involuci | ión A = A                                                                                               |

| Ley de Absorción  | A + 1 = 1                                                                                               |

| Ley de Absorcion  | A . 0 = 0                                                                                               |

| l av da Idautidad | A . 1 = A                                                                                               |

| Ley de Identidad  | A + O = A                                                                                               |

| Laurda Maneran    | $\overline{AB} = \overline{A} + \overline{B}$                                                           |

| Ley de Morgan     | $\overline{A + B} = \overline{AB}$                                                                      |

| Lav Diatributiva  | $A \cdot (B + C) = (A \cdot B) + (A \cdot C)$                                                           |

| Ley Distributiva  | $A + (B \cdot C) = (A + B) \cdot (A + C)$                                                               |

Aquí vemos un cuadro con las leyes más importantes que debemos tener a mano para recordar el álgebra de Boole.

Para entender con claridad, una tabla de verdad de una función cualquiera de N variables posee 2N filas, para un MK debe poseer 2N cuadrados. Se ordenan según su peso y el código Gray para que solo una de las variables cambie entre las celdas adyacentes.

Cuando trabajamos con circuitos, una suma de productos se realiza con dos niveles de compuertas donde cada término representa una compuerta, y cada letra del producto es una entrada de la compuerta. Es más costoso adicionar una compuerta al circuito que incluir una única compuerta con múltiples entradas. Si podemos reducir un circuito mediante MK, tendremos dos circuitos equivalentes, de los cuales el reducido será más económico ya que poseerá menos compuertas o menor número de entradas.

La propiedad más destacable de los MK es la adyacencia de las celdas (dos celdas son adyacentes si no difieren en más de un bit) debido a que, si en las dos celdas adyacentes existe un valor 1, se puede realizar la operación "factor común" de estas celdas eliminando una variable.

Para entender con claridad, una tabla de verdad de una función cualquiera de N variables posee 2N filas, para un MK debe poseer 2N cuadrados. Se ordenan según su peso y el código Gray para que solo una de las variables cambie entre las celdas adyacentes.

#### **CIRCUITOS DIGITALES**

Tabla de equivalencia entre álgebra de Boole y circuitos digitales.

El equivalente en los circuitos digitales del álgebra de Boole son compuertas lógicas que responden en función a la programación. La equivalencia entre una forma y la otra se traduce en el diseño de los circuitos electrónicos que, posteriormente, son impresos en los circuitos integrados que casi siempre utilizaremos. Los símbolos representarán las compuertas que actúan según el diseño específico.

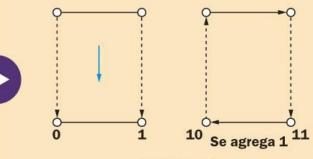

Los MK son representaciones geométricas de los números binarios; un número binario de n bits se puede representar por un punto en el espacio N. Si representamos en un plano un número binario de un bit 0 y 1, y podemos unir ambos puntos mediante una línea que los conecte, a esta unión la llamaremos **cubo 1**. Si ahora reflejamos esta figura, obtendremos un cuadrilátero. Si al primer segmento superior le agregamos un 0 a la izquierda, y al segmento inferior (el reflejado) le agregamos un 1 a la izquierda, obtenemos un nuevo **cubo 2** con cuatro vértices, correspondiente a la combinación de dos variables **(22 = 4)**. Es importante tener en cuenta que si recorremos los nuevos vértices, podremos observar cambios de una sola cifra.

El mapa de Karnaugh es uno de los métodos utilizados para la minimización de funciones algebraicas booleanas y es utilizado también para minimizar expresiones del tipo suma de productos o productos de sumas, obteniendo así otra suma de productos y otros productos de sumas. Como vimos se trata de una serie de cuadrados, donde cada cuadrado constituye una línea de la tabla de verdad. Dicha tabla se encarga de desplegar el valor de verdad de una proposición compuesta, para cada combinación de valores de verdad que se puedan establecer a sus componentes.

#### Operaciones de Álgebra de Boole

| Opera                                            | ciones                           |

|--------------------------------------------------|----------------------------------|

| Υ                                                | AND                              |

| 0 . 0 = 0<br>0 . A = 0<br>A . 0 = 0<br>A . A = A | 0.0=0<br>0.1=0<br>1.0=0<br>1.1=A |

| 0                                                | OR                               |

| A + 0 = A<br>A + 0 = 1<br>1 + A = A<br>1 + 1 = 1 | 0+0=0<br>1+0=1<br>0+1=1<br>1+1=1 |

| NO                                               | NOT                              |

| A'' = A<br>A' = A                                | $\frac{\overline{0}}{1} = 1$     |

Tabla comparativa entre las funciones del álgebra de Boole para un sistema cualquiera y un sistema binario. La variable A puede ser cualquier valor.

# USO PRÁCTICO DEL DIAGRAMA PASO A PASO...

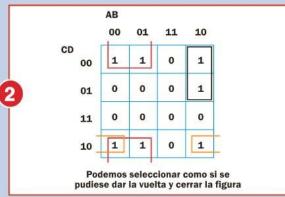

Tabla de 4 variables 16 cuadros. 8 posibles resultados 00 01 11 10 C D Fn В CD 00 1 1 0 1 01 0 0 0 1 11 0 0 0 0 10 1 1 0 1

Para comenzar armamos la tabla de verdad y posicionamos los valores de Fn en el MK.

Luego agrupamos los 1 más próximos en grupos de dos en dos, solo vertical y horizontalmente con la menor cantidad de grupos posibles.

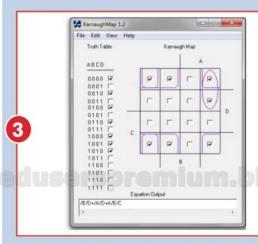

Leemos qué variables cambian dentro del rango seleccionado, hay tres rangos seleccionados, tres minitérminos. Comparemos con el programa.

// Clase 11∢

na puerta lógica o compuerta lógica es, como bien dijimos, un dispositivo electrónico que representa la expresión física de un operador booleano en la lógica de conmutación. Cada puerta lógica consiste en una red de dispositivos interruptores que cumple las condiciones booleanas para el operador particular. Son, esencialmente, circuitos de conmutación integrados en un chip.

Es necesario que aclaremos, que las compuertas lógicas se comunican entre sí (incluidos los micro-procesadores) usando el sistema binario, que consta de solo dos indicadores: 0 y 1.

Así pues, encontramos gran variedad de compuertas estándares, cada una con un comportamiento perfectamente definido, y es posible combinarlas entre sí para obtener funciones nuevas. Desde el punto de vista práctico, podemos considerar cada compuerta como una caja negra, en la que introducimos valores digitales en sus entradas, y el valor del resultado aparece en la salida.

Cada compuerta tiene su tabla de verdad, que expresa en forma de lista el estado de su salida para cada combinación posible de estados en las entradas.

La compuerta IF (SI en español) realiza la función booleana de la igualdad. En los esquemas de un circuito electrónico se simboliza mediante un triángulo, cuya base corresponde a la entrada, y el vértice opuesto, a la salida. Su tabla de verdad es sencilla: la salida siempre toma el valor de la entrada. Esto significa que, si en la entrada hay un nivel

de tensión alto, también lo habrá en su salida; y, si la entrada se encuentra en un nivel bajo, su salida también será el mismo estado. Las compuertas IF se utilizan como amplificadores de corriente para permitir manejar dispositivos que tienen consumos de corriente elevados, desde otros que solo pueden entregar corrientes más débiles.

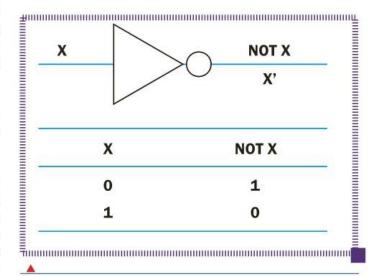

La compuerta **NOT** presenta, en su salida, un valor que es el opuesto del que está presente en su única entrada. Se simboliza en un esquema eléctrico en el mismo símbolo que la compuerta IF con un pequeño círculo agregado en su salida. Su función es la de negar, y comparte con la compuerta IF la característica de tener solo una entrada. Se utiliza cuando es necesario tener disponible un valor lógico opuesto a uno dado.

13

// Clase 11∢

La puerta lógica NOT realiza la función booleana de inversión o negación de una variable lógica. Proporciona el estado inverso del que esté en su entrada.

#### **CONJUNTO DE COMPUERTAS**

Un conjunto de puertas lógicas completo es aquel con el que se puede implementar cualquier función lógica (puertas AND, OR y NOT; AND y NOT; OR y NOT; puertas NAND y puertas NOR). Un conjunto de puertas lógicas es completo si puede implementar todas las puertas de otro conjunto completo conocido. La equivalencia funcional entre compuertas lógicas es importante en el aspecto práctico, dado que un tipo de compuerta lógica puede tener mejores características operativas que otro, dependiendo de la tecnología utilizada.

CADA COMPUERTA CONSISTE

EN UNA RED DE DISPOSITIVOS

INTERRUPTORES QUE

CUMPLE LAS CONDICIONES

BOOLEANAS PARA

EL OPERADOR.

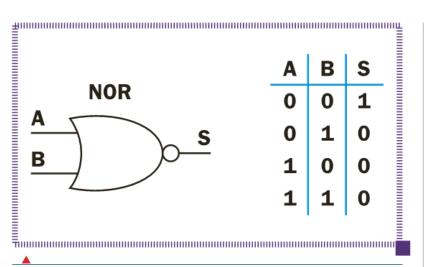

La compuerta AND, llamada Y en español, con dos o más entradas, realiza la función booleana de multiplicación. Su salida será un 1 cuando todas sus entradas también estén en nivel alto. En cualquier otro caso, la salida será un 0. El resultado de multiplicar entre sí diferentes valores binarios solo dará como resultado 1 cuando todos ellos también sean 1.

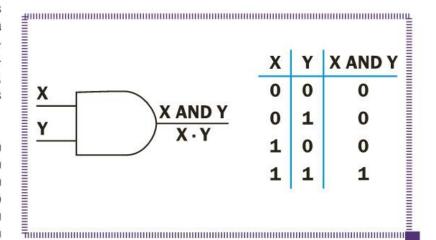

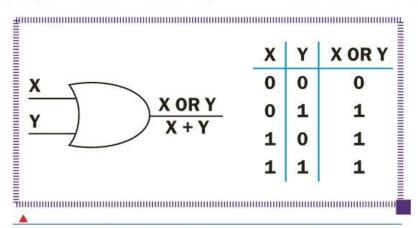

La función booleana que realiza la compuerta OR (0) es la asociada a la suma, y matemáticamente la expresamos como +. Presenta un alto estado en su salida cuando, al menos una de sus entradas, también está en estado alto. En cualquier otro estado, la salida será 0 . Tal como ocurre con las compuertas AND, el número de entradas puede ser mayor a dos.

A B S

0 0 1

A B S

1 0 1

1 1 0

Podemos definir la puerta NO-Y, o NAND, como aquella que proporciona a su salida un 0 lógico únicamente cuando todas sus entradas están a 1.

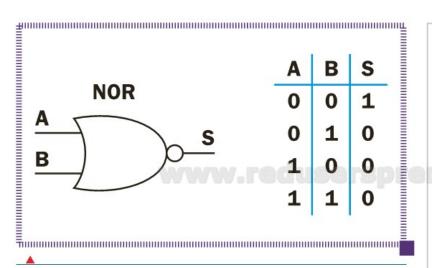

La compuerta NOR proporciona, a su salida, un 1 lógico solo cuando todas sus entradas están a 0. Constituye un conjunto completo de operadores.

La compuerta NAND (NO Y) es la negación de la compuerta AND. Cualquier compuerta lógica se puede negar agregando una compuerta NOT que realice esta tarea. Debido a que es una situación muy común, se han fabricado compuertas que ya están negadas internamente, como es el caso de la NAND. Esto modifica su tabla de verdad, y la salida solo será un 0 cuando todas sus entradas estén en 1. El número de entradas debe ser de dos como mínimo, pero no nos será extraño encontrar NAND de tres o más entradas.

La compuerta NOR (NO 0) es de forma similar a la NAND; una compuerta NOR es la negación de una compuerta OR, obtenida agregando una etapa NOT en su salida.

La salida de una compuerta NOR es 1 solamente cuando todas sus entradas son 0. Igual que en casos anteriores, la negación se expresa en los esquemas mediante un círculo en la salida. El número de entradas también puede ser mayor a dos.

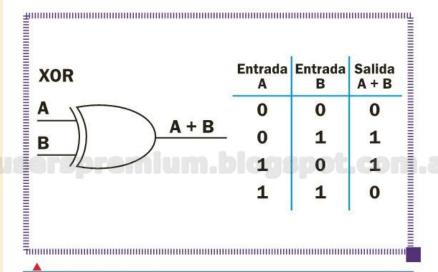

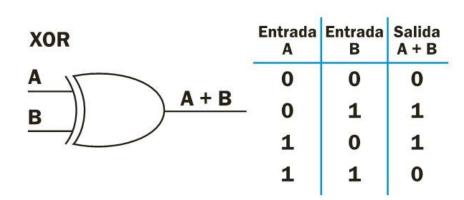

En una compuerta XOR (OR exclusiva) realiza la función booleana de A'B + AB. Esta compuerta da como resultado 1 cuando los valores en las entradas son distintos (por ejemplo en una puerta de dos entradas). Si la puerta tuviese tres o más entradas, la XOR tomaría la función de suma de paridad: cuenta el número de unos a la entrada y, si resulta un número impar, pone un 1 a la salida para que el número de unos pase a ser par. Esto se debe a que la operación XOR es asociativa.

Finalmente, mencionaremos la compuerta NXOR (No o Exclusivo), que no es más que una compuerta XOR con su salida negada, por lo que su salida estará en estado alto solo cuando sus

LA MAYORÍA DE LAS CENTRALES ELÉCTRICAS QUE EXISTEN HOY EN DÍA EN EL MUNDO TRANSFORMAN ENERGÍA MECÁNICA EN EL ÉCTRICA.

La compuerta AND, llamada Y en español, con dos o más entradas, realiza la función booleana de multiplicación. Su salida será un 1 cuando todas sus entradas también estén en nivel alto. En cualquier otro caso, la salida será un 0. El resultado de multiplicar entre sí diferentes valores binarios solo dará como resultado 1 cuando todos ellos también sean 1.

La función booleana que realiza la compuerta OR (0) es la asociada a la suma, y matemáticamente la expresamos como +. Presenta un alto estado en su salida cuando, al menos una de sus entradas, también está en estado alto. En cualquier otro estado, la salida será 0 .Tal como ocurre con las compuertas AND, el número de entradas puede ser mayor a dos.

A B S

0 0 1

1 0 1

1 1 0

Podemos definir la puerta NO-Y, o NAND, como aquella que proporciona a su salida un 0 lógico únicamente cuando todas sus entradas están a 1.

La compuerta NOR proporciona, a su salida, un 1 lógico solo cuando todas sus entradas están a 0. Constituye un conjunto completo de operadores.

La compuerta NAND (NO Y) es la negación de la compuerta AND. Cualquier compuerta lógica se puede negar agregando una compuerta NOT que realice esta tarea. Debido a que es una situación muy común, se han fabricado compuertas que ya están negadas internamente, como es el caso de la NAND. Esto modifica su tabla de verdad, y la salida solo será un 0 cuando todas sus entradas estén en 1. El número de entradas debe ser de dos como mínimo, pero no nos será extraño encontrar NAND de tres o más entradas.

La compuerta NOR (NO 0) es de forma similar a la NAND; una compuerta NOR es la negación de una compuerta OR, obtenida agregando una etapa NOT en su salida.

La salida de una compuerta NOR es 1 solamente cuando todas sus entradas son 0. Igual que en casos anteriores, la negación se expresa en los esquemas mediante un círculo en la salida. El número de entradas también puede ser mayor a dos.

En una compuerta XOR (OR exclusiva) realiza la función booleana de A'B + AB. Esta compuerta da como resultado 1 cuando los valores en las entradas son distintos (por ejemplo en una puerta de dos entradas). Si la puerta tuviese tres o más entradas, la XOR tomaría la función de suma de paridad: cuenta el número de unos a la entrada y, si resulta un número impar, pone un 1 a la salida para que el número de unos pase a ser par. Esto se debe a que la operación XOR es asociativa.

Finalmente, mencionaremos la compuerta NXOR (No o Exclusivo), que no es más que una compuerta XOR con su salida negada, por lo que su salida estará en estado alto solo cuando sus

LA MAYORÍA DE LAS

CENTRALES ELÉCTRICAS

QUE EXISTEN HOY EN DÍA

EN EL MUNDO TRANSFORMAN

ENERGÍA MECÁNICA

EN ELÉCTRICA.

entradas son iguales y, en estado bajo, para las demás combinaciones posibles.

La máquina de Turing es un dispositivo de reconocimiento de lenguajes, que manipula símbolos de acuerdo con una tabla de reglas. A pesar de su simplicidad, puede ser adaptada para simular la lógica de cualquier algoritmo de computadora.

Dicha máquina tiene un control finito, una cabeza lectora y una cinta donde puede haber caracteres, y donde eventualmente viene la palabra de entrada. La cinta es de longitud infinita hacia la derecha, hacia donde se extiende en forma indefinida, y los espacios se llenan con el carácter blanco. La cinta no es infinita hacia la izquierda, por lo que hay un cuadro de la cinta que es el extremo izquierdo; la cabeza lectora es de lectura y escritura, por lo que la cinta puede ser modificada en curso de ejecución. Además, la cabeza se mueve bidireccionalmente (izquierda y derecha), por lo que puede pasar repetidas veces sobre un mismo segmento de la cinta.

Este modelo está conformado por un alfabeto de entrada y uno de salida, un símbolo especial llamado blanco, un conjunto de estados finitos y un conjunto de transiciones entre dichos estados. Su funcionamiento se basa en una función de transición, que recibe un estado inicial y una cadena de caracteres (la cinta, la cual es finita por la izquierda) pertenecientes al alfabeto de entrada. Luego va leyendo una celda de la cinta, borrando el símbolo, escribe el nuevo símbolo perteneciente al alfabeto de salida y, por último, avanza a la izquierda o a la derecha (solo una celda a la vez), repitiendo esto según se indique en la función de transición, para finalmente detenerse en un estado final o de aceptación, que represente la salida.

La máquina de Turing consta de un cabezal lector/escritor y de una cinta infinita en la que el cabezal lee el contenido, borra el contenido anterior y escribe un

#### MÁQUINA DE TURING

La máquina de Turing puede considerarse como un autómata capaz de reconocer lenguajes formales. En ese sentido, puede reconocer los lenguajes recursivamente enumerables, de acuerdo a la jerarquía de Chomsky. Su potencia es, por tanto, superior a otros tipos de autómatas, como el autómata finito o el autómata con pila, o igual a otros modelos con la misma potencia computacional.

LAS COMPUERTAS LÓGICAS SE

COMUNICAN ENTRE SÍ USANDO EL

SISTEMA BINARIO, QUE CONSTA DE SOLO

DOS INDICADORES: 0 Y 1.

Conocida por su nombre en inglés AND, la compuerta Y realiza la función booleana de producto lógico. Su símbolo es un punto, aunque se suele omitir.

nuevo valor. Las operaciones que se pueden realizar en esta máquina se limitan a: avanzar el cabezal lector/escritor hacia la derecha y avanzar el cabezal lector/ escritor hacia la izquierda. El cómputo es determinado a partir de una tabla de estados de la forma: (estado, valor) (nuevo estado, nuevo valor, dirección).

Esta tabla toma como parámetros el estado actual de la máquina y el carác-

ter leído de la cinta, y da la dirección para mover el cabezal, el nuevo estado de la máquina y el valor que será escrito en la cinta.

Mediante este modelo teórico y el análisis de complejidad de algoritmos, fue posible la categorización de problemas computacionales de acuerdo con su comportamiento; así, aparece el conjunto de problemas denominados P y NP, 15

// Clase 11 4

16

►Clase 11 //

EN SU VERSION ORIGINAL,

LA MÁQUINA DE TURING

CONSISTE EN UNA CINTA

INFINITAMENTE LARGA CON

UNOS Y CEROS.

#### **TURING**

Turing, en 1948, definió su máquina como "... una ilimitada capacidad de memoria obtenida en la forma de una cinta infinita marcada con cuadrados, en cada uno de los cuales podría imprimirse un símbolo. En cualquier momento, hay un símbolo en la máguina, llamado el símbolo leído. La máquina puede alterar el símbolo leído, y su comportamiento está en parte determinado por ese símbolo, pero los símbolos en otros lugares de la cinta no afectan el comportamiento de la máquina. Sin embargo, la cinta se puede mover hacia adelante y hacia atrás a través de la máquina, lo que constituye una de sus operaciones elementales".

La compuerta OR puede ser definida como aquella que proporciona a su salida un 1 lógico si, al menos una de sus entradas, está a 1.

cuyas soluciones en tiempo polinómico son encontradas según el determinismo y no determinismo, respectivamente, de la máquina de Turing.

De hecho, se puede probar en forma matemática que, para cualquier programa de computadora, es posible crear una máquina de Turing equivalente.

#### **Funcionamiento**

Ahora nos preguntamos: ¿cómo funciona? Es un dispositivo que transforma un INPUT en un OUTPUT; tanto el INPUT como el OUPUT constan de números en código binario (ceros y unos). En su versión original, la máquina de Turing consiste en una cinta infinitamente larga con unos y

ceros, que pasa a través de una caja. La caja es tan fina que solo el trozo de cinta que ocupa un bit (0 o 1) está en su interior. La máquina tiene una serie de estados internos finitos que también se pueden numerar en binario.

Para llevar a cabo algún algoritmo, la máquina se inicializa en algún estado interno arbitrario. A continuación, se pone en marcha, y la máquina lee el bit que se encuentra en ese momento en su interior; luego, ejecuta alguna operación con ese bit (lo cambia o no, dependiendo de su estado interno). Después, se mueve hacia la derecha o hacia la izquierda, y vuelve a procesar el siguiente bit de la misma manera.

Imagen que refleja los elementos, partes y sectores de un generador de corriente alterna en las centrales eléctricas.

Una familia lógica es un conjunto de circuitos integrados compatibles entre sí, que se alimentan con el mismo voltaje y entienden los mismos niveles lógicos. Como consecuencia, las salidas de las puertas pueden conectarse directamente a las entradas de otras puertas de la misma familia sin ningún problema de adaptación ni de comunicación entre sí.

Una familia lógica va a estar determinada por el tipo de componente con que está construida, y la estructura básica con que se construyen las compuertas lógicas, así como sus valores.

## Familias lógicas

Los circuitos integrados, como ya sabemos, se pueden clasificar en analógicos y digitales. Los circuitos integrados digitales funcionan con la base de la lógica booleana o álgebra de Boole, en la que cada operación es representada en electrónica digital por una compuerta lógica.

Algunos circuitos son considerados por su nivel de complejidad, es decir, por el número de puertas que estos contienen, y los fabricantes han desarrollado familias lógicas de dispositivos digitales que representan 0 y 1, por medio de parámetros eléctricos. En estos se definen propiedades de operación, como niveles de tensión y corriente, disipación de potencia, retardos de propagación, fan-out, entre otras.

Una familia lógica es el conjunto de circuitos integrados (Cl's) los cuales pueden ser interconectados entre si sin ningún tipo de Interfase o aditamento, es decir, una salida de un Cl puede conectarse directamente a la entrada de otro Cl de una misma familia. Se dice entonces que son compatibles.

Las familias pueden clasificarse en bipolares y MOS, podemos mencionar algunos ejemplos de familias bipolares: RTL, DTL, TTL, ECL, HTL, IIL. y de familias MOS: PMOS, NMOS, CMOS. Las tecnologías TTL y CMOS (metal oxido-semiconductor complementario) son los mas utilizadas en la fabricación de SSI (baja escala de integración) y MSI (media escala de integración).

## MOSQUITOS PASO A PASO

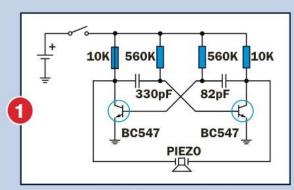

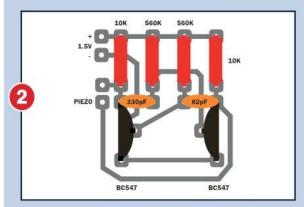

Diagrama circuital del ahuyentador. El corazón de este circuito consta de dos transistores NPN BC547, que se consiguen fácilmente en cualquier casa de electrónica.

Otro vistazo, pero ahora cómo sería el diseño para PCB, de fácil implementación en un PCB virgen de 2,5 x 2,5 cm.

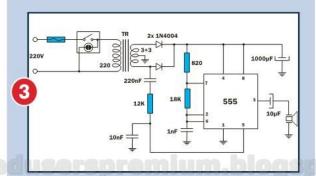

Circuito PLUS. Acá podemos ver otro diseño de un ahuyentador, en este caso implementado con un CI 555, en el que las resistencias regulan la oscilación del circuito. 17

// Clase 11∢

La compuerta XOR es aquella que proporciona un 1 lógico, solo si las dos entradas son iguales. Es verdadero si ambos componentes tienen el mismo valor lógico

Según el diseño y el montaje del sistema digital, el tipo de transistor u otros componentes electrónicos utilizados, se conocen dos tipos de familias lógicas. Por lo general, el tipo de componente usado en la construcción del circuito lleva el nombre de la tecnología utilizada, y cada familia está formada por subfamilias.

La primera familia que mencionaremos es la **bipolar**; esta emplea transistores bipolares (BJT), resistencias y diodos, es decir, dispositivos de unión. De esta familia, la más representativa es la **familia TTL**.

La familia TTL es caracterizada por su rapidez. Es saturante porque los transistores que la forman trabajan en corte-saturación (conmutación). Esa corriente de base elevada conlleva a que, cuando se desea pasar al corte, el exceso de carga acumulada en la base tarda en desalojarse, lo que contribuye a tiempos de conmutación mayor. Una de las mejoras introducidas en la familia TTL estándar es la utilización de un transistor de entrada multie-

misor, que favorece el paso de saturación al de corte, retirando la carga almacenada en la base del transistor durante la saturación. De esta familia, surgen variadas series, como la **74Sxxx**; esta trata de evitar que los transistores alcancen el estado de saturación, reduciendo así el exceso de carga en la zona de base. De esta forma, tarda menos en conmutar de saturación a corte, aumentando considerablemente la velocidad.

La serie **74LSxxx** es una mejora de la familia **74Sxxx**, la cual obtenía un gran aumento de velocidad respecto de la TTL estándar, a costa del aumento de las corrientes circulantes por las puertas.

LA FAMILIA TTL ES

SATURANTE PORQUE

LOS TRANSISTORES QUE

LA FORMAN TRABAJAN

EN CORTE-SATURACIÓN

(CONMUTACIÓN).

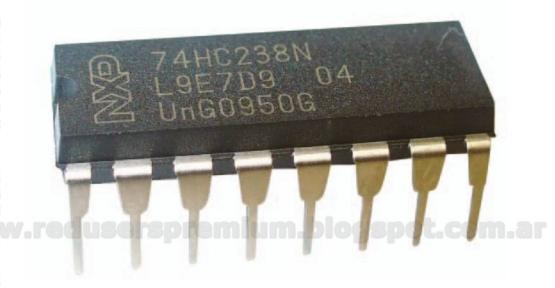

Set de cuatro compuertas NAND (TTL), una de las primeras diseñadas en el mercado de la electrónica digital; fueron remplazadas por las NAND CMOS. La segunda familia por nombrar es la MOSFET. Estas familias emplean transistores MOSFET (transistores de efecto campo). Las más representativas son las familias NMOS, PMOS y CMOS. Puntualmente hablaremos de la familia CMOS.

Existen varias series en la familia CMOS de circuitos integrados digitales. La serie 4000 y la 14000 fueron las primeras. También existe la serie 74C cuya característica principal es ser compatible terminal por terminal y función por función con los dispositivos TTL. Esto hace que sea posible reemplazar algunos circuitos TTL por un diseño equivalente CMOS.

La serie **74HC** está integrada por los CMOS de alta velocidad, que tienen un aumento de diez veces en la velocidad de conmutación. La serie **74HCT** es también de alta velocidad y compatible en lo que respecta a los voltajes con los dispositivos TTL.

Los voltajes de alimentación en la familia CMOS tienen un rango muy amplio; estos valores van de 3 a 15V para los 4000 y los 74C. De 2 a 6V para los 74HC y 74HCT.

Por lo tanto, los márgenes de ruido se pueden determinar y llegan a ser de 1,5V. Esto es mejor que los TTL, ya que los CMOS pueden ser utilizados en medios con mucho más ruido. Los márgenes de ruido pueden hacerse todavía mayores si aumentamos el valor de VDD, ya que es un porcentaje de este.

En lo que a la disipación de potencia concierne, tenemos un consumo de potencia de solo 2,5 nW cuando VDD = 5V y, cuando VDD = 10V, la potencia consumida aumenta a solo 10 nW.

De esta forma podemos darnos cuenta que el aumento en el consumo no es considerable, teniendo en cuenta la potencia de consumo a la que nos estamos enfrentando, la cual aumenta desde 2,5 nW a tan solo 10 nW.

#### **MÁRGENES DE RUIDO**

#### **PROYECTADO**

Cuanto mayor sean los márgenes de ruido, los circuitos serán menos sensibles a las perturbaciones; se adecuarán para trabajar en entornos con mayor índice de ruido.